# Where the Noise Starts – PWB Design –

Thurman J. (Bill) Ritenour EMC Compliance, LLC 4545 Laguna Place #160 Boulder, Colorado 80303 (303) 543-7404 emccomply@aol.com

January 24, 2000

### REFERENCES

- [1] Personal Communications (Michael King):

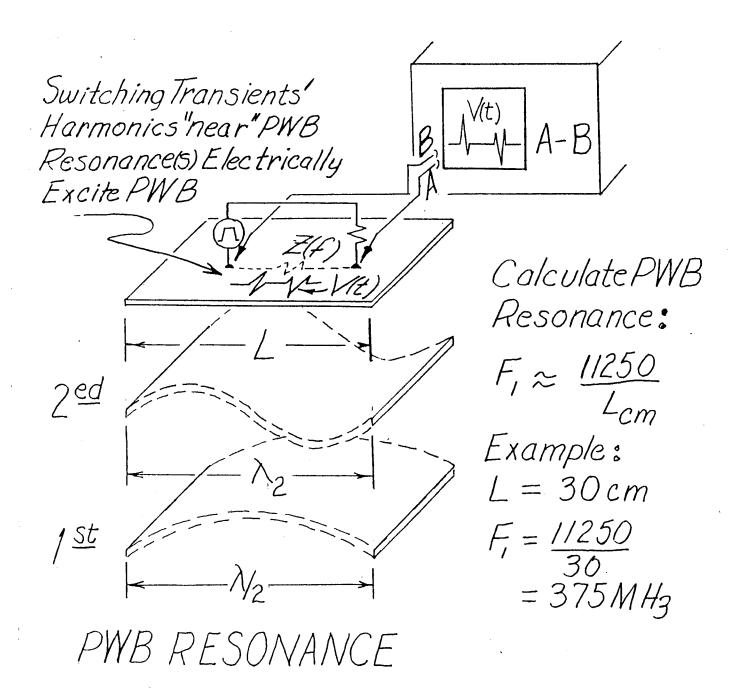

- •August 1987 –Discussions concerning PWB Board Resonance phenomenon with respect to its effect on Common-mode (CM) currents, as well as CM current minimization via appropriate PWB-to-chassis grounding and connector placement.

- •August 1991 –Discussions on CM current generation effects due to reference planes cuts located under signal traces along with an explanation of PWB inductance, also the effect of vias and traces on decoupling capacitor resonance as well as signal trace "Reference Flipping".

- [2] Ott, Noise Reduction Techniques in Electronic Systems, Pages 296 and 297, Wiley and Sons 1988, ISBN 0-471-85068-3.

- [3] Dockey, "Asymmetrical Mode Radiation from Multi-layer Printed Circuit Boards", pages 247 251, Conference Proceedings of EMC/ESD International Symposium, Denver Colorado, April 22-24, 1992, published by Cardiff Publishing Company.

- [4] Dockey & German, "New Techniques for Reducing Printed Circuit Board Common-mode Radiation", pages 334 339, Proceedings 1993 IEEE Symposium on Electromagnetic Compatibility, Dallas, Texas August 9-13, 1993.

- [5] Leferink & Van Doorn, "Inductance of Printed Circuit Board Ground Planes", pages 327 329, *Proceedings 1993 IEEE Symposium on Electromagnetic Compatibility*, Dallas, Texas August 9-13, 1993.

- [6] Ott, "Ground Plane Inductance", Paper presented to Rocky Mountain Chapter, EMC Society 1994

- [7] Leferink, "Reducing Radiation Emissions by the Application of SNT", page 469, *Proceedings 1994 IEEE Symposium on Electromagnetic Compatibility*, Chicago, Illinois August 22-26, 1994.

- [8] Holloway and Kuester, "Net and Partial Inductance of a Microstrip ground Plane", *IEEE Transactions on Electromagnetic Compatibility*, volume 40, number 1, pages 33-45, 1998.

- [9] Ott, "Ground Plane Inductance [update]", Paper presented at: EMC '99 ARIZONA A Colloquium and Exhibition on Pre-Compliance EMC Testing problems and Solutions sponsored by Phoenix chapter of the IEEE EMC, May 1999.

## **PWB TOPICS**

- Board and Board plus Cable Resonance

- Ground Plane Inductance

- Ground Plane Inductance "Drivers" (The Noise Makers)

- Mitigation Techniques (as time and interest permits)

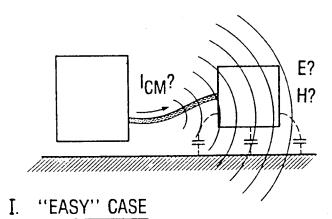

# CM RADIATION FROM I/O CABLES

V<sub>S</sub> Z<sub>W</sub> R<sub>L</sub> V<sub>A</sub> CM

RADIATION CAUSED BY THE I/O SIGNAL ITSELF

Extracted from Interference Control Technology lecture notes (created approximately 1987).

Author was Michel Mardiguian.

- THE LARGEST UNBALANCED CURRENT COMES FROM THE "HOT" SIDE OF R<sub>L</sub> (UNLESS THE WHOLE SYSTEM IS PERFECTLY BALANCED)

- THEREFORE A GOOD APPROXIMATION OF ICM IS:

$$I_{CM} \approx \frac{V_A}{Z_{Loop}} = \frac{V_S}{Z_W + Z_{float}}$$

WHERE  $Z_{float}$  IS the circuit to ground impedance of load side; if the load is grounded, the loop impedance is minimal

• RADIATION IS COMPUTED USING VS, ZLOOP AND LOOP AREA AS INPUTS

-

△"Electromagnetic Shielding", Page 9.14; VOL 3, ICT EMC Series, 1988

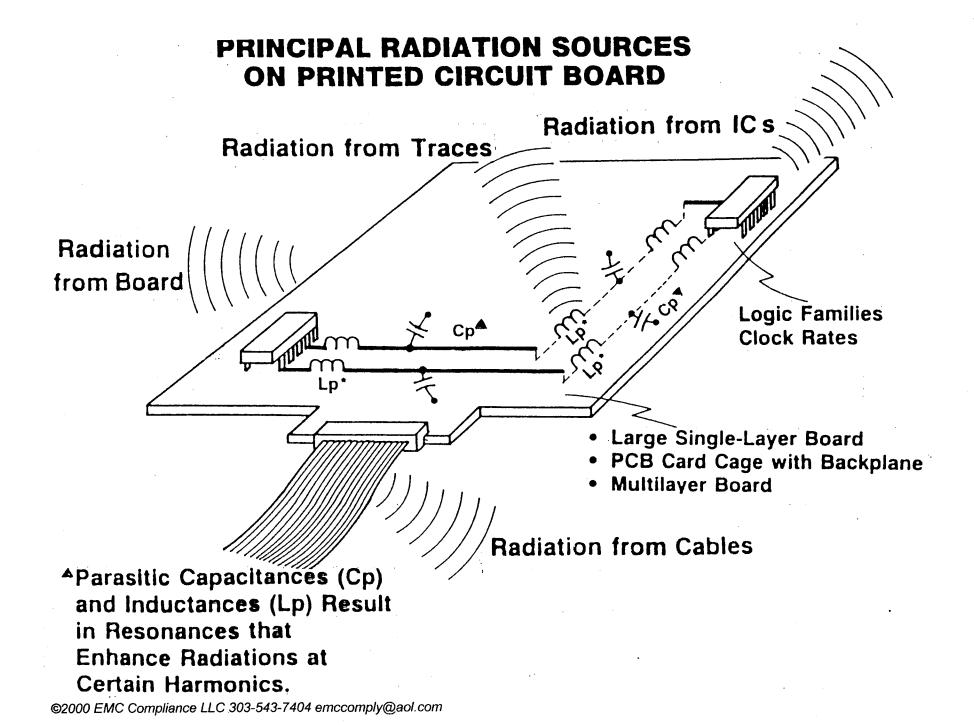

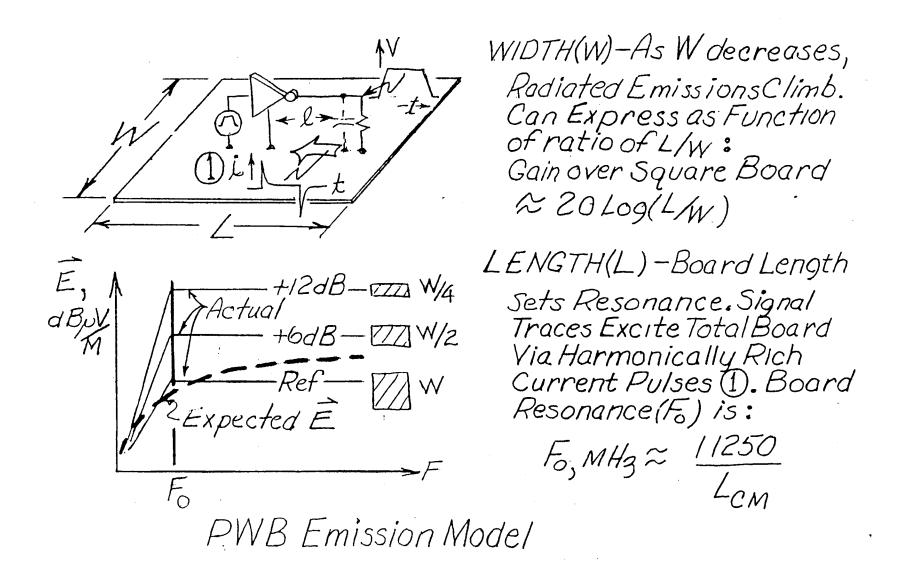

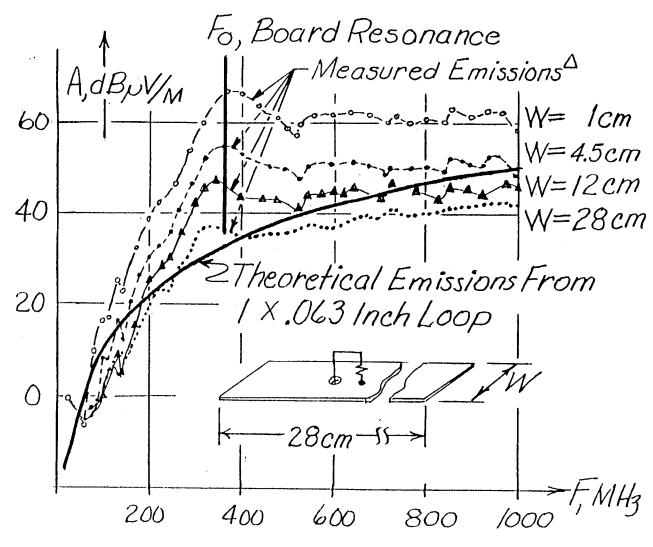

PWB Length-to-Width Effects on Emissions

Asymetrical Mode Radiation From Multi-Layer Printed Circuit Boards"

R. Dockey, 1991 EMC-ESD Conference Proceedings, Cardiff Publishina

©2000 EMC Compliance LLC 303-543-7404 emccomply@aol.com

CABLE Radiation Concept

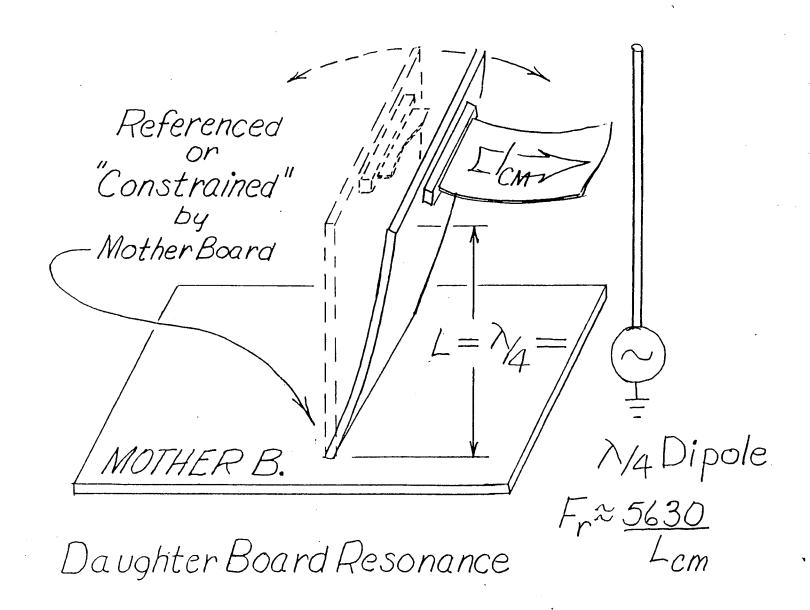

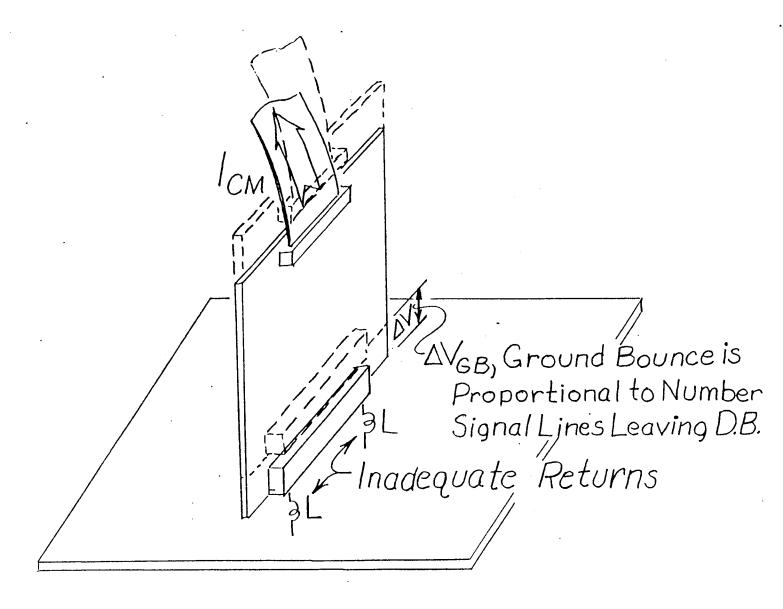

Daughter Board Ground Bounce

555555555 RSR5R5R5R 55555555

One Ret. to 5Sig.

One Ret. to 2 Sig.

RSRSRSRSR SRSRSRSRSRSRSRSRSR

One Ret. to 1 Sig.

Slow Signals - More than 15 nS Rise Time △V<sub>GB</sub> < 200mV @15 nS

Medium Signals-MoreThan 5nS RiseTime, Less Than 15nS △VGB≤250mV@5nS

Fast Signals-Less Than 5nS Rise Time, More Than 2nS  $\Delta V_{GB} \leq 300 \, \text{mV} \otimes 2nS$

Selecting Connector Returns (Grounds)

# Common-Mode (CM) Current

- IC Switching Induced CM Current

- Capacitor Decoupling Induced CM Current

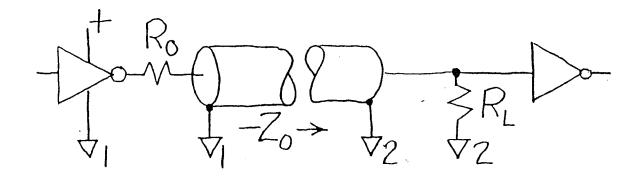

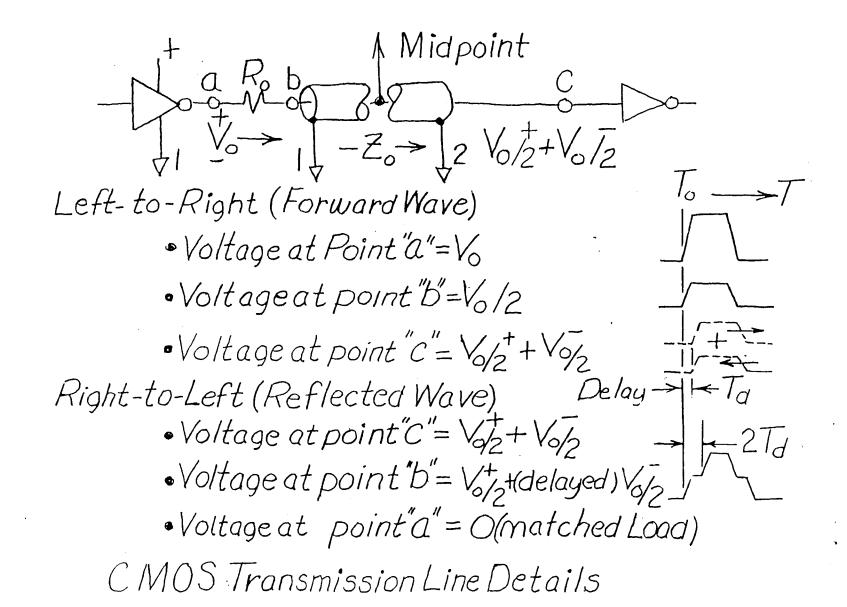

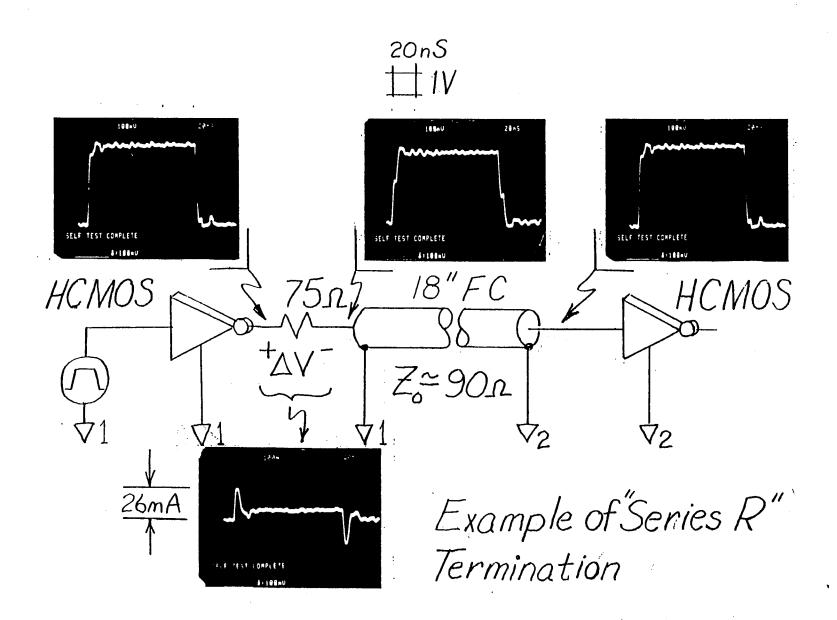

- Transmission line Induced CM Current

- Connector Induced CM Current

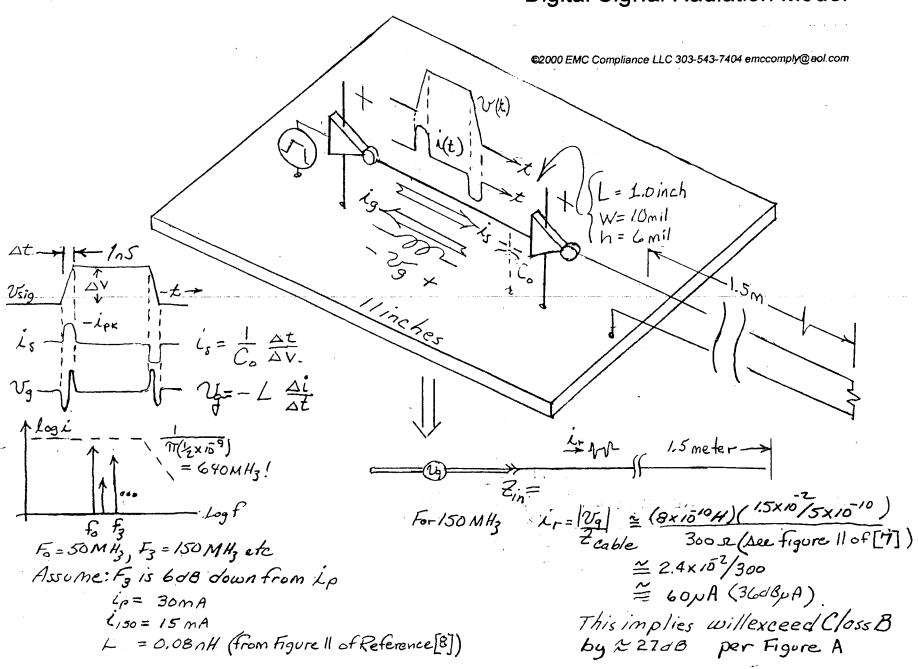

### Simple Illustrative Model of Ground Plane plus Digital Signal Radiation Model

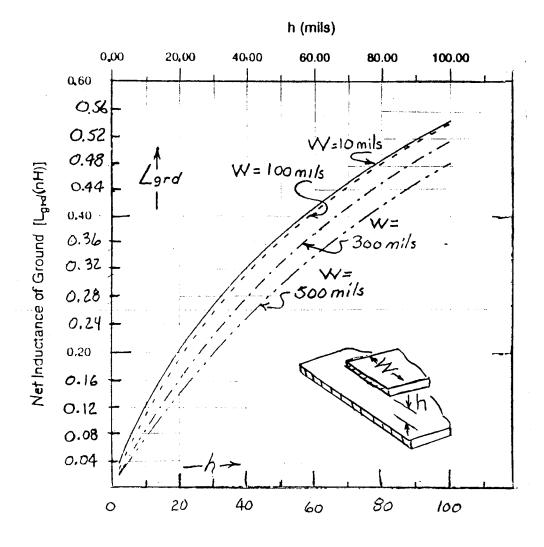

Net Ground Plane Inductance as a Function of Signal Trace Width (w) and Height (h) above the Ground Plane for a 1 inch Trace [ref 8]

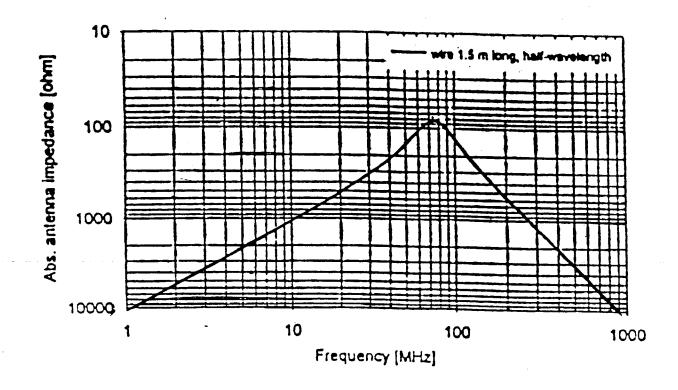

Antenna Input Impedance of a 1.5 meter Long Cable at Half Wave Resonance [ref 7]

# Figure A—Table of EN55022 Class B Maximum Allowable Common Mode Cable Currents for Information Technology Equipments

The table below shows the maximum *common mode current* that–flowing along the various lengths of cable shown and at the stated frequencies–will cause far field emissions<sup>1</sup> equal to EN55022 Class B limits<sup>2</sup>

| cable   | Quarter    | Max. Non-  | Max. Non-  | Max. Non-  | Max. Non-              | Max. Non-              |

|---------|------------|------------|------------|------------|------------------------|------------------------|

| length, | Wave       | Fail       | Fail       | Fail       | Fail                   | Fail                   |

| meters  | Resonance  | Current At | Current At | Current At | Current At             | Current At             |

|         | Frequency, | 30 MHz,    | 60 MHz,    | 120 MHz,   | 240 MHz <sup>2</sup> , | 480 MHz <sup>2</sup> , |

|         | MHz        | dBuA       | dBuA       | dBuA       | dBuA                   | dBuA                   |

| 0.1     | 750        | 44         | 38         | 32         | 33                     | 27                     |

| 0.2     | 375        | 38         | 32         | 26         | 27                     | 21                     |

| 0.5     | 150        | 30         | 24         | 18         | 19                     | 13                     |

| 1.0     | 75         | 24         | 18         | 12         | 13                     | 7                      |

| 2.0     | 38         | 18         | 12         | 6          | 7                      | 1                      |

<sup>1)</sup>  $E=(2\pi \ 10^{-7} \ x \ F \ x \ L \ x \ I) \ / \ D$  (see C. Paul, Introduction to Electromagnetic Compatibility , page 417, equation 8.21), where:

E-absolute value of field strength in volts/meter maximized with respect to antenna polarity and cable aspect

F-frequency in Hz

L-length of cable in meters

I –common mode current flowing along cable in Amperes

D-distance from cable to antenna in meters

2) EN55022 emission limits at 10 meters are 30 dBuV/m from 30 MHz to 230 MHz and increase by 7 dB for frequencies above 230 MHz

# **Decoupling Capacitors**

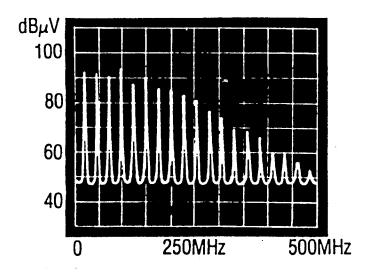

- Chip Cross-Over Current

- Rise Time

- Capacitor Lead Inductance,

- Parasitic Inductance

- Series Resonance

- Dynamic Impedance, Δe/Δi

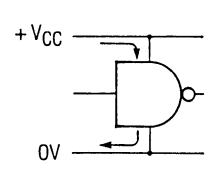

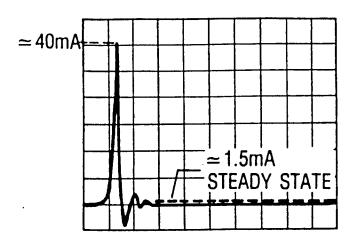

# POWER SUPPLY TRANSITION CURRENT 74LS GATE

SCALE: HORIZONTAL—5ns/div; VERTICAL—7mA/div

SPECTRUM MEASURED WITH TEKTRONIX PROBE (TRANSFER IMPEDANCE  $5\Omega$ )

Cross-Over Current

Late = 2.1 nH

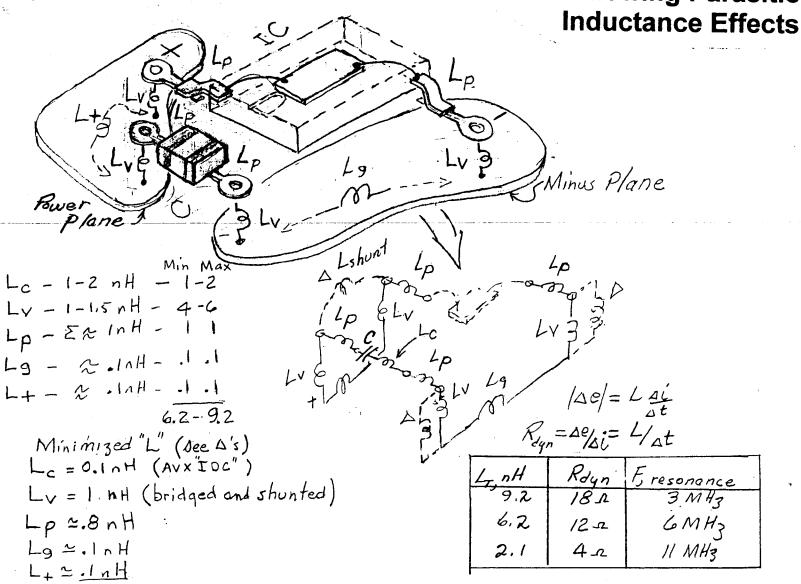

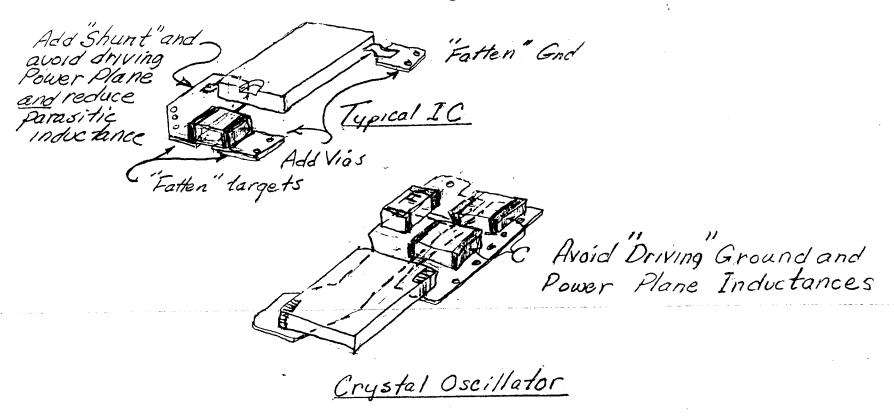

# Visualization Sketch of Typical Decoupling Capacitor Circuit Showing Parasitic Inductance Effects

Minimize Parasitic Inductance

# Alternate Methods of Minimizing Decoupling Parasitic Inductance and Reducing "Board Bounce"

# Low Inductance Chip Capacitors

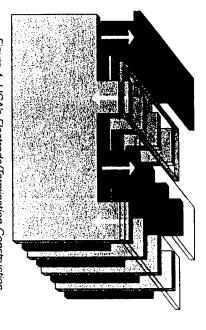

# Low Inductance Chip Arrays (LICA\*)

Figure 4. LICA's Electrode/Termination Construction.

The current path is minimized – this reduces self-inductance.

Current flowing out of the positive plate, returns in the opposite direction along the adjacent negative plate – this reduces the mutual inductance.

Also the effective current path length is minimized because the current does not have to travel the entire length of both electrodes to complete the circuit. This reduces the self-inductance of the electrodes. The self-inductance is also minimized by the fact that the charging current is supplied by both sets of terminals reducing the path length even further! The inductance of this arrangement is less than 100 pH, causing the self-resonance to be above 50 MHz for the same popular 100 nF capacitance. Parts available in the LICA design are shown on pages 6 and 7.

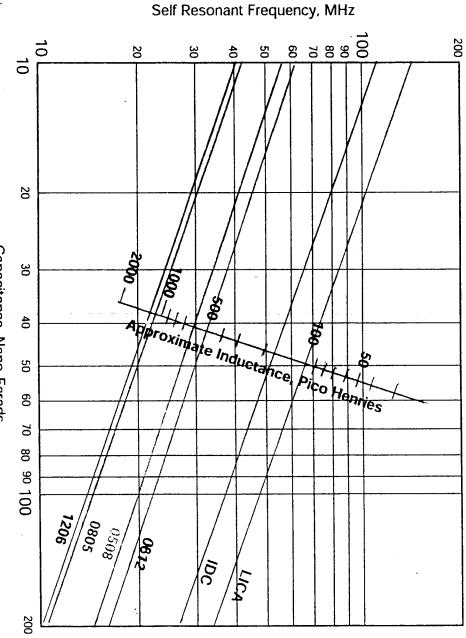

Figure 5 compares the self resonant frequencies of various capacitor designs versus capacitance values. The approximate inductance of each style is also shown.

Active development continues on low inductance capacitors. C4 termination with low temperature solder is now available for plastic packages. Consult AVX for details.

Self Resonant Frequencies vs. Capacitance and Capacitor Design Capacitance, Nano-Farads

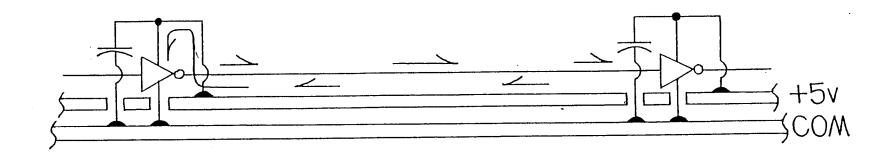

Case 1-Signal Referenced to Power Plane (+5v)

# Case 2-Signal Referenced to Common Plane

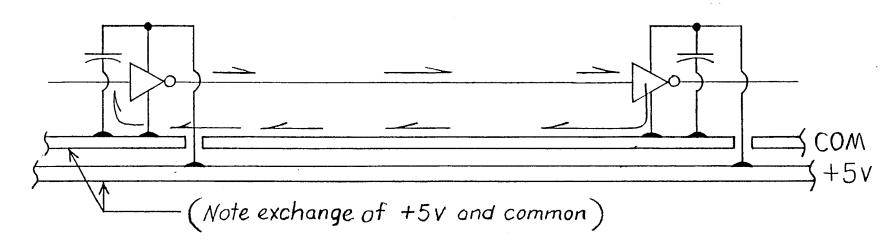

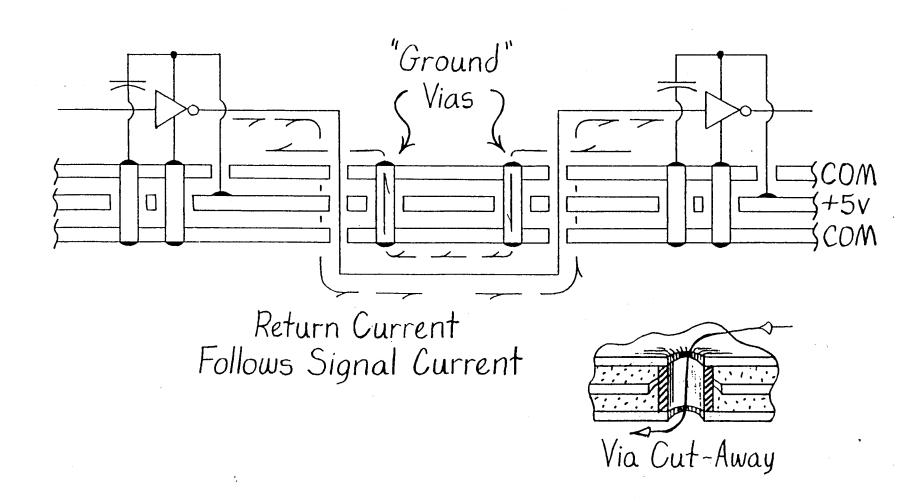

Case 3-Signal References BOTH

5 Volts & Common

Cis never large enough - causes follow the source?

Signal Delay and NOISE

This question becomes important ONLY if signal rise time falls below 5 ns

# Fix For Case 3-Add Extra Common

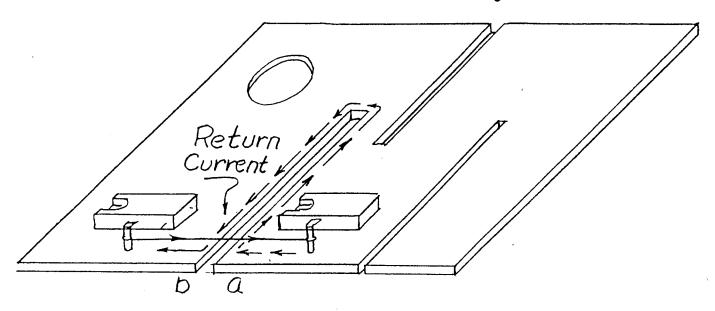

# "Detours" in Ground Plane Cause:

- Inductive Hitson Zo

High Frequency Emissions

Beware of Chopped Ground Plane

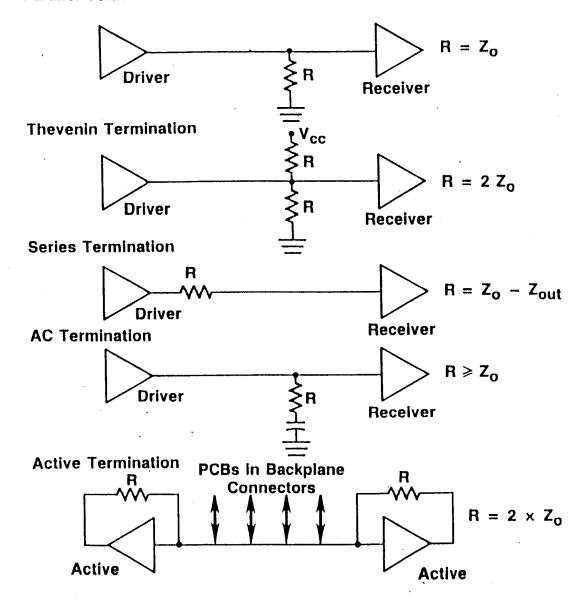

- For Bipolar Logic, Goal is to "Match"  $R_L$  to  $Z_0$  so that Reflection = 0

- For CMOS Logic, Goal is to Match Roto  $Z_0$  and Set  $R_L = \infty$  so that Reflection = +1

Concept of Transmission Line Matching

### **Parallel Termination**

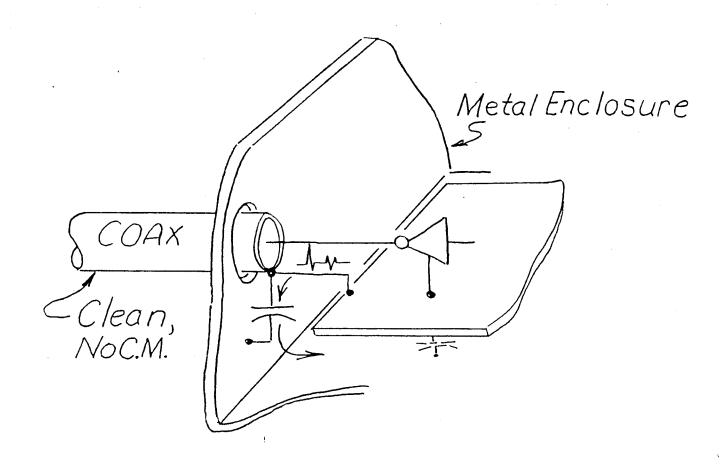

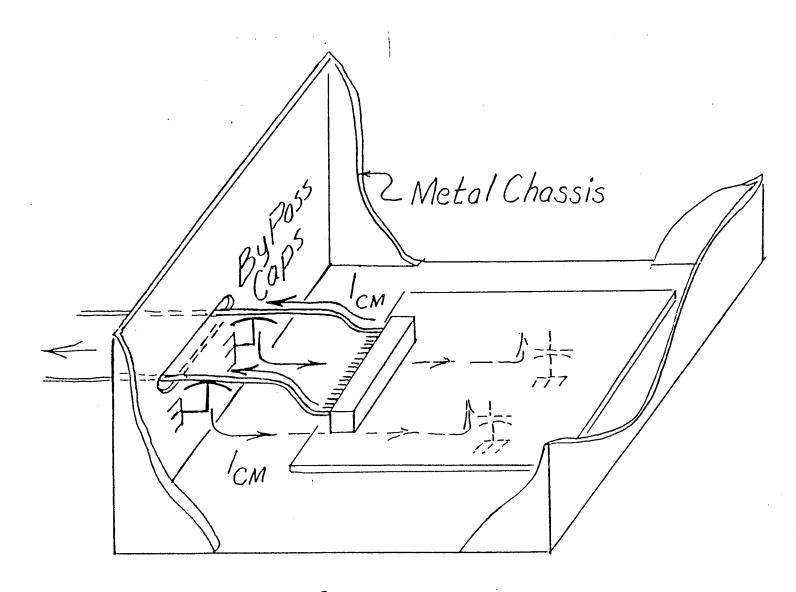

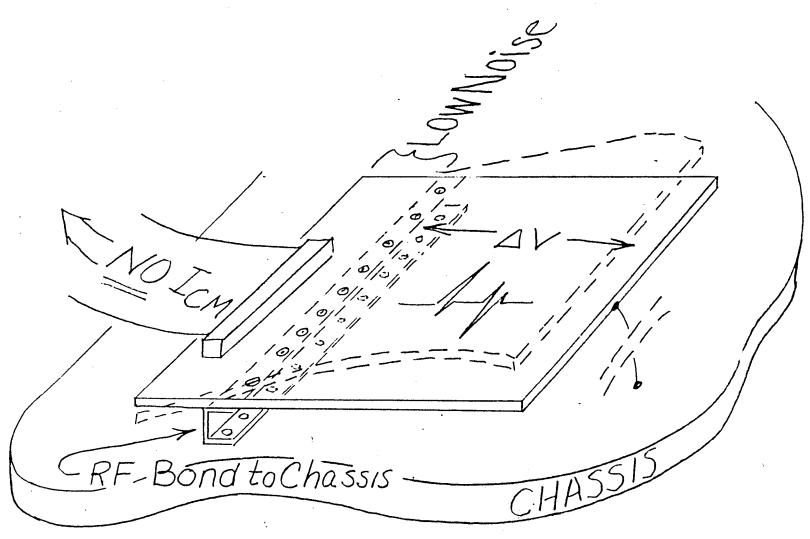

How to Decouple Common Mode Current to Chassis and Preserve HF

Decoupling Common Mode Currents at the Chassis

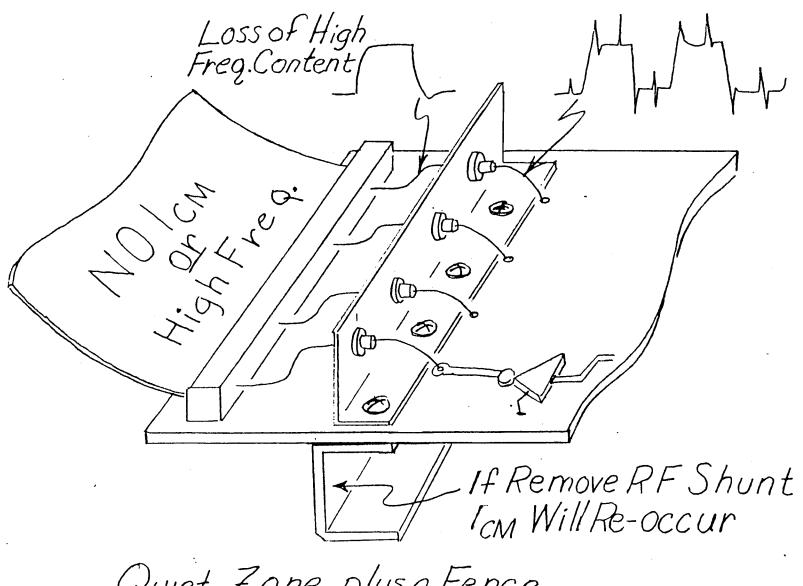

Quiet Zone plusa Fence

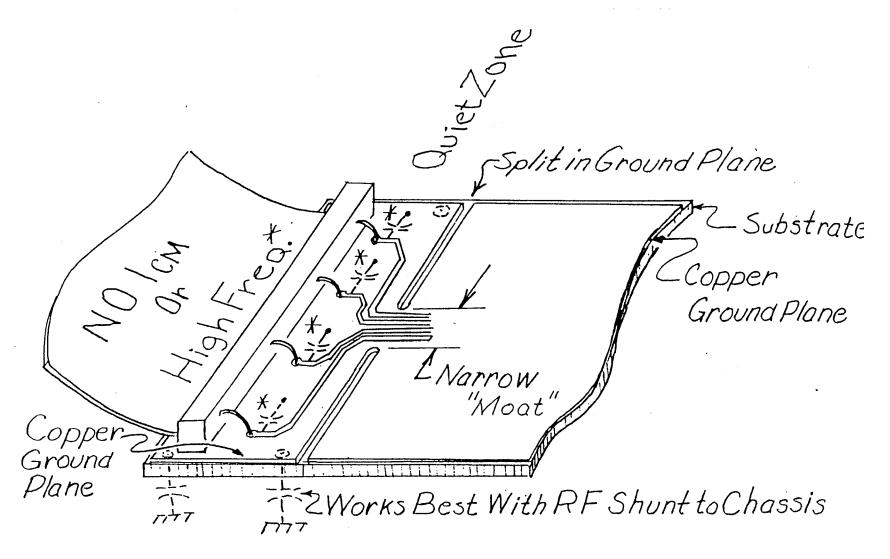

Alternate Quiet Zone-The Moat

Establishing a PWB LowNoise Zone