## Power Distribution System Decoupling— "how 'bout them vias?"

Presented by

Thurman J. (Bill) Ritenour

EMC Compliance LLC

4875 Sioux Drive #303

Boulder, Colorado 80303 USA

303.543.7404

emccomply@aol.com

Ansoft Calculations and Curves Preparation by

Charles (Chas) Grasso Senior EMC Engineer EchoStar 303-706-5467

prepared for

Rocky Mountain Chapter of the EMC Society of the IEEE January 23, 2003

- INTRODUCTION (Where we are and where we seem to be going)

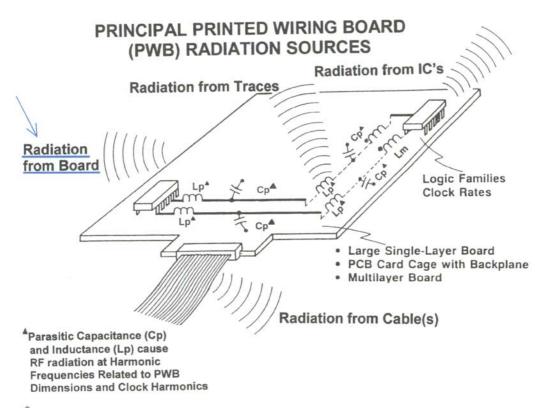

- WHERE THE NOISE STARTS (and SI and EMI become intertwined)

- PWB DECOUPLING (One of the several necessary ways to control noise)

- VIAS (today, yesterday and tomorrow)

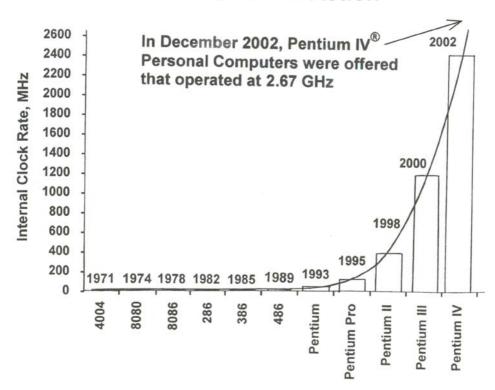

In 1972 Gordon Moore, co-founder of Intel Corporation predicted that the performance of computers would double every 18 months<sup>1</sup>. Over the last 21 years, the rate of development of computers based on that prediction has held firm.

At the time of Mr. Moore's prediction, the first Intel 4004<sup>™</sup> microprocessor slogged along at a 108 KHz rate and contained 2300 transistors. On May 6, 2002 IBM™ announced its latest Intel Pentium IV® driven Computer. Its clock rate is 2400 MHz, and it is reported to contain over 10 million transistors. It is apparent that the progression of computer development up to the present day has closely followed Mr. Moore's prediction. In fact, by the late fall of 2002 Dell <sup>™</sup> and others began offering Pentium IV's® operating at 2670 MHz.

The rate of electronic design complexity is accelerating too. New designs must incorporate new features in order to allow them to operate at ever increasing speeds. Signal Integrity and Electromagnetic Compatibility are key elements in the feature development process.

3

#### Moore's Law in Action

<sup>© 2003</sup> EMC Compliance LLC 4875 Sioux Drive #303, Boulder, Colorado 80303 303.543.7404 emccomply@aol.com

<sup>&</sup>lt;sup>1</sup> Page 4, "High Speed Digital System Design—A handbook of Interconnect theory and Design", Hall, Hall and McCall, Copyright 2000 by Wiley and Sons, ISBN 0-471-36090-2

<sup>© 2003</sup> EMC Compliance LLC 4875 Sioux Drive #303, Boulder, Colorado 80303 303.543.7404 emccomply@aol.com

#### 5

#### Semiconductor Device Speed-Where Are We Today?<sup>1</sup>

#### One Example of Leading Edge Integrated Circuit Technology is composed of Heterojunction Bipolar transistors

- <u>Device Technology:</u> Silicon-Germanium (SiGe) Heterojunction Bipolar transistors (HBT)

- Process: 0.13 um with copper interconnects and 50 Ohm internal T-Lines

- Vendor: IBM Microelectronics

- · HBT Transistor/Circuit Capabilities:

HBT Transistor F<sub>t</sub> 285 GHz Equivalent Gate Delay 4.23 ps Demonstrated Toggle Rate: 110 GHz

NOTE: this technology will be available commercially before the end of 2002

April 1,2002, Electronic Design Magazine (US Edition), page 27

© 2003 EMC Compliance LLC 4875 Sioux Drive #303, Boulder, Colorado 80303 303.543,7404 emccomply@aol.com

- INTRODUCTION (Where we are and where we seem to be going)

- WHERE THE NOISE STARTS (and SI and EMI become intertwined)

- PWB DECOUPLING (One of the several necessary ways to control noise)

- VIAS (today, yesterday and tomorrow)

<sup>© 2003</sup> EMC Compliance LLC 4875 Sioux Drive #303, Boulder, Colorado 80303 303.543.7404 emccomply@aol.com

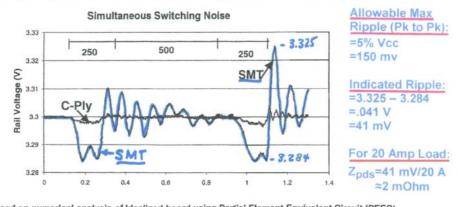

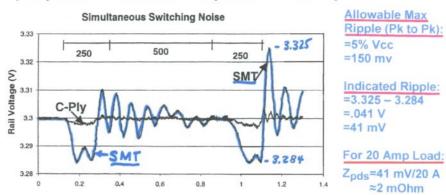

#### PWB Power Supply Noise Ripple Comparison for Surface Mount (SM) and Embedded Capacitor Decouplers\*

PWB Width: Via Length:

**SMT Capacitor:**

C-Ply Capacitor:

**Driving Signal:**

Logic Family:

4 inches (1 cm) 1 mm (to Vcc), 0.5 mm (to Common)

0.96 nF (1206) 0.96 nF (embedded)

1 nS duration 250 pS rise and fall time 3.3 Volt supply with five deep 0.5 um CMOS Cells followed by simple inverter

▲ Diaz-Alvarez et al: MODELING AND SIMULATION OF INTEGRATED CAPACITORS, pages 611-619, IEEE Transactions on Components and Packaging Technologies, December 2000

<sup>© 2003</sup>EMC Compliance LLC 4875 Sloux Drive #303, Boulder, Colorado 80303 303.543.7404 emccomply@aol.com

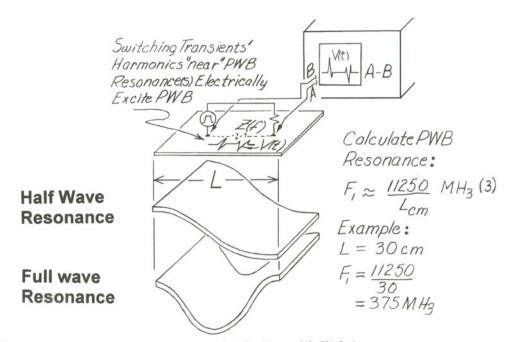

#### PWB RESONANCE ILLUSTRATION

[3] Dockey, "Asymmetrical Mode Radiation from Multi-layer Printed Circuit Boards", pages 247 – 251, Conference Proceedings of EMC/ESD International Symposium, Denver Colorado, April 22-24, 1992, published by Cardiff Publishing Company

<sup>2003</sup> EMC Compliance LLC 4875 Sioux Drive #303, Boulder, Colorado 80303 303.543.7404 emccomply@aol.com

- INTRODUCTION (Where we are and where we seem to be going)

- WHERE THE NOISE STARTS (and SI and EMI become intertwined)

- PWB DECOUPLING (One of the several necessary ways to control noise)

- VIAS (today, yesterday and tomorrow)

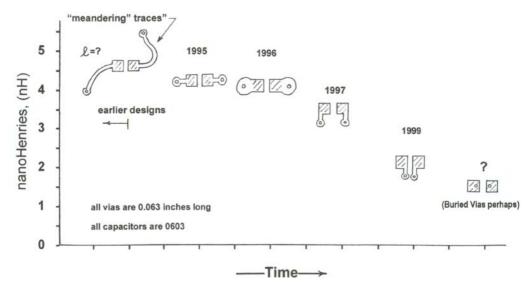

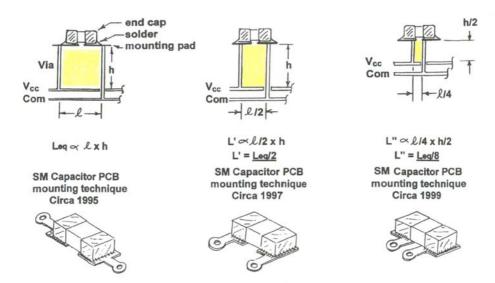

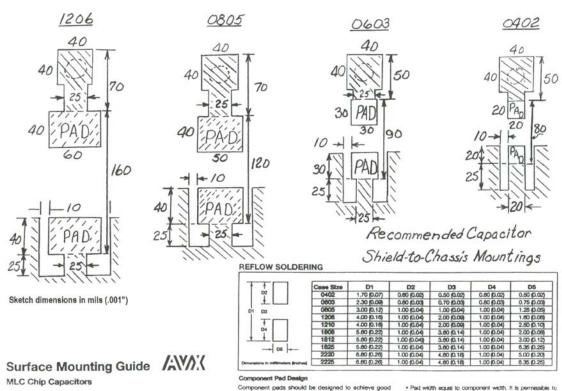

Surface Mount (SM) Decoupling Capacitor PCB

Mounting Techniques—Shortened Trace Length and

Via Location—used to Reduce Equivalent Series

Inductance (ESL)<sup>1</sup>

<sup>&</sup>lt;sup>1</sup> Adopted from "ESR and ESL of Ceramic Capacitor Applied to Decoupling Applications"; Tanmoy Roy, Larry Smith, and John Prymak; IEEE Electrical Performance of Electronic Packaging Conference; August 1998

<sup>© 2003</sup> EMC Compliance LLC 4875 Sioux Drive #303, Boulder, Colorado 80303 303.543.7404 emccomply@aol.com

### Reducing SM Decoupling Capacitor PCB Assembly Equivalent Inductance by Minimizing Via Separation and Via Length<sup>1</sup>

<sup>&</sup>lt;sup>1</sup>Adopted from "Power Distribution System Design Methodology and Capacitor Selection for Modern CMOS Technology", Larry Smith, et. al., IEEE Transactions on Advanced Packaging, Vol. 22, No. 3, August 1999

<sup>© 2003</sup> EMC Compliance LLC 4875 Sioux Drive #303, Boulder, Colorado 80303 303.543.7404 emccomply@eol.com

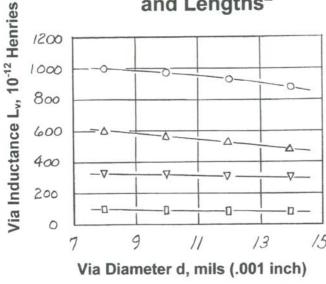

h= 80 mils

h=60 mils

h=25 mils

h=10 mils

<sup>5</sup>Extracted from AVX Corporation Document: INTERCONNECT SCHEMES FOR LOW INDUCTANCE CERAMIC CAPACITORS, Published April 1999 (available from www.avxcorp.com)

© 2003 EMC Compliance LLC 4875 Sioux Drive #303, Boulder, Colorado 80303 303.543.7404 emccomply@aol.com

#### PWB Power Supply Noise Ripple Comparison for Surface Mount (SM) and Embedded Capacitor Decouplers

Curves based on numerical analysis of Idealized board using Partial Element Equivalent Circuit (PEEC) formulation-

PWB Length:

4 inches (1 cm)

PWB Width: Via Length:

**Driving Signal:**

Logic Family:

4 inches (1 cm) 1 mm (to Vcc), 0.5 mm (to Common)

**SMT Capacitor:** C-Ply Capacitor:

0.96 nF (1206) 0.96 nF (embedded)

1 nS duration 250 pS rise and fall time

3.3 Volt supply with five deep 0.5 um CMOS Cells followed by simple inverter

Diaz-Alvarez et al: MODELING AND SIMULATION OF INTEGRATED CAPACITORS, pages 611-619, IEEE Transactions on Components and Packaging Technologies, December 2000

<sup>©2003</sup>EMC Compliance LLC 4875 Sioux Drive #303, Boulder, Coloredo 80303 303,543,7404 emccomply@aol.com

#### 16

# Low Inductance Chip Capacitors

Low Inductance Chip Arrays (LICA\*)

current path is minimized - this reduces self-inductance Current flowing out of the positive plate, returns in the Figure 4. LICA's Electrode/Termination Construction. opposite direction along the adjacent negative plate this reduces the mutual inductance.

mized by the fact that the charging current is supplied by causing the self-resonance to be above 50 MHz for the same popular 100 nF capacitance. Parts available in the Viso the effective current path length is minimized because The inductance of this arrangement is less than 100 pH. electrodes to complete the circuit. This reduces the sell inductance of the electrodes. The self inductance is also min both sets of terminals reducing the path length even further JCA design are shown on pages 6 and 7.

IX

19000

1000

100

10

1

0.1

0.01

0.001

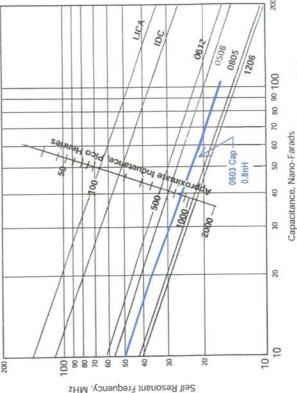

Figure 5 compares the self resonant frequencies of various capacitor designs versus capacitance values. The approxinate inductance of each style is also shown

Active development continues on low inductance is now available for plastic packages. Consult AVX capacitors. C4 termination with low temperature solder

104

Single

Tantalum Cap

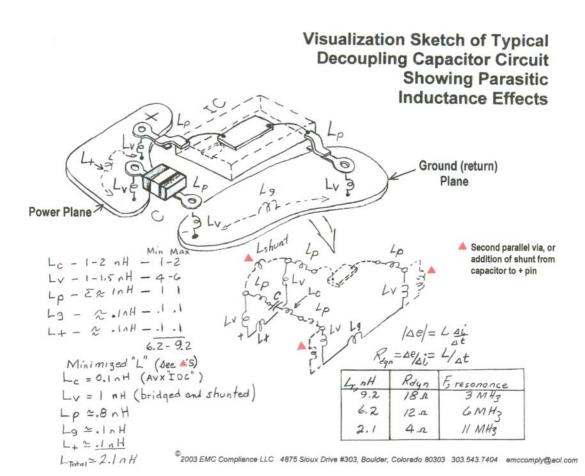

Conceptual Sketch Showing Surface Mount Capacitor Parasitic Inductance Effects

Theoretical

"Q"Effect

© 2003 EMC Compliance LLC 4875 Sloux Drive #303, Boulder, Colorado 80303 303 543 7404 emccomply@aol.com

F 43

Single 0603 Ceramic Cap

Desired PDS Impedance

Self Resonant Frequencies vs. Capacitance and Capacitor Design

Curve shown courtesy of AVX Corp

INTRODUCTION (Where we are and where we seem to be going)

.

WHERE THE NOISE STARTS (and SI and EMI become intertwined)

.

- PWB DECOUPLING (One of the several necessary ways to control noise)

- VIAS (today, yesterday and tomorrow)

18

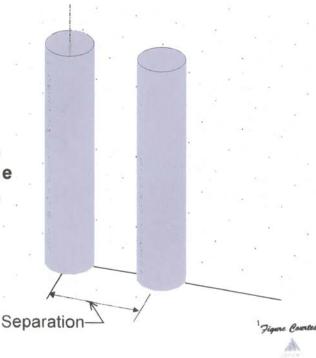

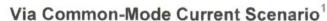

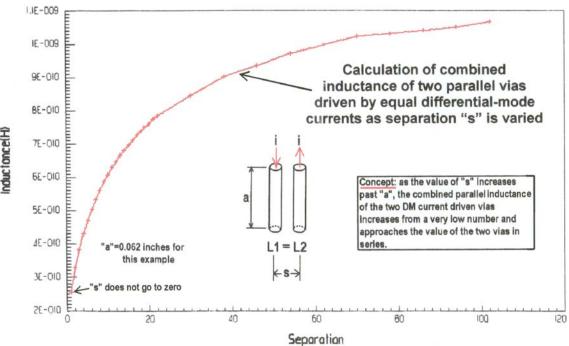

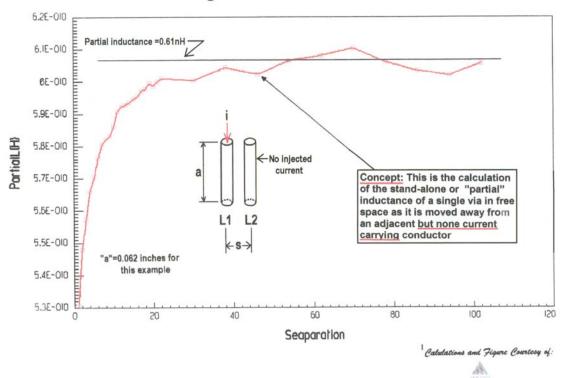

#### Two Via Simulation Model

Via diameter: 15 mils Via height: 62 mils Via separation: variable

Simulation model of two vias embedded in a plane — Note absence of pads.

<sup>© 2003</sup> EMC Compliance LLC 4875 Sioux Drive #303, Boulder, Colorado 80303 303.543,7404 emccomply@aol.com

© 2003 EMC Compliance LLC 4875 Sloux Drive #303, Boulder, Colorado 80303 303.543,7404 emccomply@aol.com

20

#### Via Differential Current Scenario<sup>1</sup>

Robotations and Time Pornters of

Ah

<sup>© 2003</sup> EMC Compliance LLC 4875 Sioux Drive #303, Boulder Coloredo 80303 303,543,7404 emcc cmply@aol.com

#### Single "Stand-Alone" Via Scenario<sup>1</sup>

<sup>© 2003</sup> EMC Compliance LLC 4875 Sioux Drive #303, Boulder, Colorado 80303 303.543.7404 emcc amply@aol.com

solder filets and minimize component movement during reflow soldering. Pad designs are given below for the most common sizes of mutilityer commic capacitors for both winer and reflow soldering. The basis of these designs is:

<sup>© 2003</sup> EMC Compliance LLC 4875 Sioux Drive #303, Boulder, Colorado 80303 303.543.7404 emccomply@aol.com

Pad width equal to component width. It is permissible to decrease this to as low as 85% of component width but it is not advisable to go below this.

<sup>\*</sup> Pad overlap 0.5mm beneath component.

Pad extension 0.5mm beyond components for reflow and 1.0mm for wave soldering.

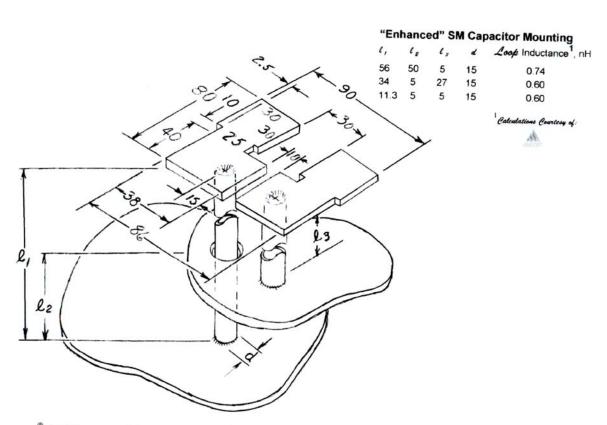

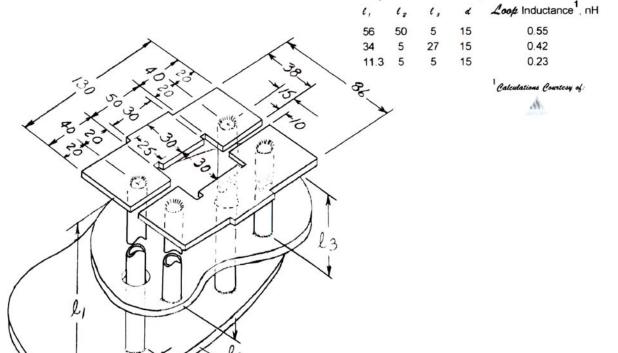

#### "Standard" SM Capacitor Mounting l, Look Inductance 1, nH 50 5 1.10 15 40 5 27 15 1.54 11.3 15 0.83 h

lз

L,

© 2003 EMC Compliance LLC 4875 Sioux Drive #303, Boulder, Colorado 80303 303.543.7404 emccomply@aol.com

© 2003 EMC Compliance LLC 4875 Sioux Drive #303, Boulder, Colorado 80303 303.543.7404 emccomply@aol.com

#### "Optimized" SM Capacitor Mounting

<sup>© 2003</sup> EMC Compliance LLC 4875 Sioux Drive #303, Boulder, Colorado 80303 303.543.7404 emccomply@aol.com